10G全硬件UDP/TCP 网络加速协议栈是一款低资源、高灵活性的网络加速IP,采用FPGA内部逻辑为客户实现高速传输,网络数据采集、存储提供相应的网络协议栈加速。该IP无需CPU参与,解决了高速网络数据环境下由于CPU中断过多、负载过大与多并发等造成的数据处理与传输的设计困难。

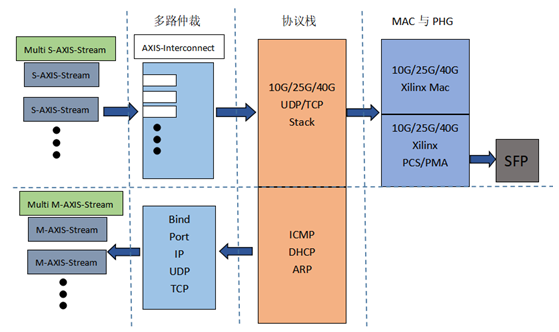

IP采用全硬件流水线化设计,采用AXIS-Stream做为数据接口,可通过AXIS-Interconnect单元快速实现任意多路的点对点/组播/广播的数据发送与接受。

IP针对Xilinx的相应系列器件进行了深度优化,大幅减小了所需资源,并根据客户的使用场景,提供了灵活的接口,以便于客户的快速集成与使用。

根据行业软硬结合的发展趋势,创新性的采样Filter+旁路的相应模式,并扩展出三种应用模型:

1 | 可作为无CPU,纯FPGA逻辑下的Udp数据收发协议栈。 |

2 | 使处理器与FPGA可同时使用单一网络接口进行数据收发,同时可过滤FPGA测高速,密集的数据流,大幅降低CPU负载,而FPGA测也通过处理器测的扩展,使其应用变得更为灵活,保留了处理器与FPGA对于网络数据处理的各自优越性。客户可使用FPGA内通道进行相对固定应用模式的高速数据收发/处理,同时可使用处理器进行相对低速,但复杂的应用协议开发,并可将本地PL测如端口,地址,路由等的管理任务交由处理器管理。 |

3 | 由于采用了axis总线,客户亦可结合DMA模型,将该协议栈作为网络协议加速器,使处理器对于相关Udp/Tcp协议打包与解析的操作于FPGA内部完成,此种应用模型下客户本地处理器应用的网络数据收发将转化为简单而高效的内存DMA操作,大幅提升原有处理器网络性能,使得其突破本身单处理器模型下的应用瓶颈。 |

产品特性:

◆ | 灵活性:支持无CPU,协同CPU,网络加速器三种应用模型 |

◆ | 支持协议:IPv4, UDP, ARP (for Request and Reply), ICMP,TCP |

◆ | 协同处理器:可配合Xilinx Zynq系列扩展完整的Linux网络协议栈(Zynq7000系列速率1Gbps,Zynq MP 2Gbps),配合使用,提供更为强大的灵活性。 |

◆ | 兼容AXI-S总线协议:可通过AXIS-INTERCONNECT 任意扩展连接数目 |

◆ | 支持组播模式 |

◆ | 兼容AXI总线 |

◆ | 支持巨大帧 |

◆ | 支持用户模式的ARP管理,客户可根据需求扩展 |

◆ | 快速项目集成 |

◆ | 少量资源,无器件限制 |

◆ | 可根据需求,选择TCP或UDP协议栈独立使用 |

结构框图: